- 您现在的位置:买卖IC网 > Sheet目录1996 > HSP45106JC-33Z (Intersil)IC OSC NCO 33MHZ 84-PLCC

5

FN2809

.8

October

16,

200

8

ENPOREG

R.ENPOREG

ENPHAC

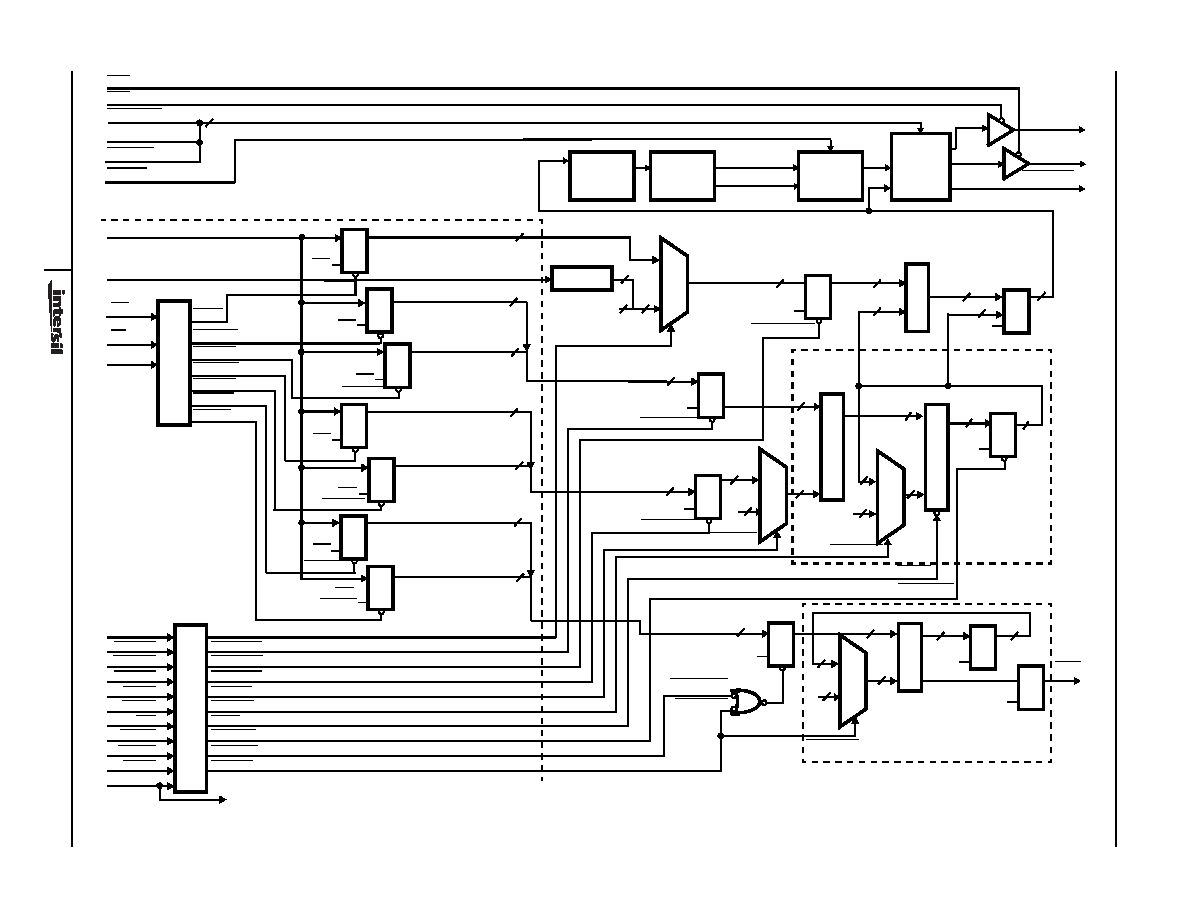

FIGURE 1. BLOCK DIAGRAM OF THE HSP45106

'0'

A(2:0)

MOD(2:1)

OES

BINFMT

OEC

R.ENPHAC

28

16

R

E

G

R.ENOFREG

R.ENCFREG

R.ENPHAC

R.ENTIREG

R.INHOFR

R.INITPAC

R.PMSEL

R.PACI

R.INITTAC

ENOFREG

ENCFREG

ENTIREG

INHOFR

INITPAC

PMSEL

PACI

INITTAC

CLK

D

E

C

O

D

E

PHEN

MSCFEN

LSCFEN

MSOFEN

LSOFEN

MSTIEN

LSTIEN

WR

CS

C(15:0)

ENCODER

R.ENPHAC

R.ENCFREG

A

D

E

R

R.PMSEL

R.INITPAC

R.INHOFR

R.ENOFREG

A

D

E

R

R.INITTAC

R.ENTIREG

R.ENPOREG

A

D

E

R

32

A

D

E

R

16

MSBs

PHEN

PHASE

PHASE INPUT

CENTER

OFFSET

TIMER

REGISTER

32

PHASE OFFSET

3

13

16

'0'

32

CENTER

REGISTER

32

'0'

32

16

LSBs

PHASE OFFSET

FREQUENCY

ADDER

32

PHASE

REGISTER

32

TICO

32

'0'

LSCFEN

LSOFEN

MSTIEN

LSTIEN

PHASE

ACCUMULATOR

SECTION

TIMER

ACCUMULATOR

SECTION

32

OFFSET FREQUENCY

REGISTER

R.PACI

16

INPUT SECTION (DISCRETE CONTROL INPUT SIGNALS

AND PROCESSOR CONTROL INTERFACE)

MSB CENTER

LSB

16

MSB OFFSET

LSB OFFSET

MSB TIMER INCREMENT

LSB TIMER

16

FREQUENCY

INCREMENT

REGISTER

ADDER

FREQUENCY

INCREMENT CLK

FORMAT

CONTROL

ADDRESS

16 COS

16 SIN

OUTPUT

CONTROL

/

16

/

16

SIN/COS

SIN/COS ARGUMENT

/

28

/

20

ACCUMULATOR

DACSTRB

COS(15:0)

SIN(15:0)

WR

>

16

0

1

MUX

CLK

R

E

G

>

CLK

R

E

G

>

CLK

R

E

G

>

R

E

G

>

CLK

R

E

G

>

CLK

R

E

G

>

R

E

G

>

R

E

G

>

R

E

G

>

R

E

G

>

R

E

G

>

R

E

G

>

WR

R

E

G

>

R

E

G

>

R

E

G

>

CLK

0

1

MU

X

0

1

MUX

0

1

MUX

CLK

INPUT REG (16)

FREQUENCY INPUT

REG (16)

CENTER

FREQUENCY

INPUT REG (16)

FREQUENCY INPUT

REG (16)

FREQUENCY

INPUT REG (16)

INCREMENT INPUT

REG (16)

DECODE

ROM

PAR/SER

TEST

3

HSP45106

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

HSP45116AVC-52Z

IC OSC NCO 52MHZ 160-MQFP

ICL7109EPL+

IC ADC 12BIT 3-ST 40-DIP

ICM7217AIPI

IC OSC UP/DWN CNTR 2MHZ 28-DIP

ICM7217CIPI

IC OSC UP/DWN CNTR 2MHZ 28-DIP

ICM7242IPA

IC OSC BINARY CTC 13MHZ 8-DIP

ICM7250IWE+T

IC OSC BINARY CTC 15MHZ 16SOIC

ICM7556IPD

IC OSC TIMER DUAL 500KHZ 14-DIP

ICM7556MJD

IC OSC TIMER DUAL 1MHZ 14DIP

相关代理商/技术参数

HSP45106JI-25

制造商:Rochester Electronics LLC 功能描述:- Bulk

HSP45116

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Numerically Controlled Oscillator/Modulator

HSP45116 WAF

制造商:Intersil Corporation 功能描述:

HSP45116/883

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Numerically Controlled Oscillator/Modulator

HSP45116_04

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Numerically Controlled Oscillator/Modulator

HSP45116883

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Numerically Controlled Oscillator/Modulator

HSP45116A

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Numerically Controlled Oscillator/Modulator

HSP45116A_07

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Numerically Controlled Oscillator/Modulator